- Home

- Companies

- Zurich Instruments AG

- Products

- Zurich Instruments - Model HDAWG - 750 ...

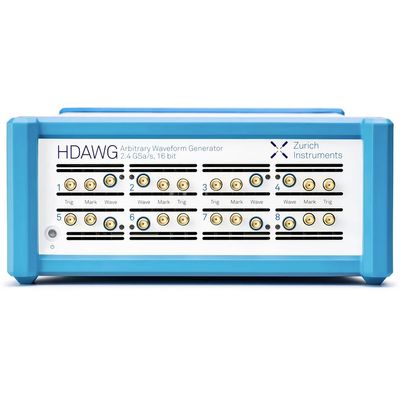

Zurich Instruments - Model HDAWG -750 MHz Arbitrary Waveform Generator

The Zurich Instruments HDAWG multi-channel Arbitrary Waveform Generator has the highest channel density available in its class, and is designed for advanced signal generation up to 750 MHz bandwidth. The HDAWG comes with either 4 or 8 DC-coupled, single-ended analog output channels with 16-bit vertical resolution. Output switching is supported between a direct mode with maximized bandwidth and superior noise performance and an amplified mode that boosts the signal amplitude to a maximum of 5 Vpp. Temporal synchronization of up to 18 HDAWGs is supported through the PQSC.

LabOne provides a state-of-the-art programming concept that combines the performance and flexibility of an arbitrary waveform generator with the accessibility of a function generator. The LabOne user interface and a choice of APIs for Python, C, MATLAB®, LabVIEW™ and .NET enable measurement automation and fast integration into an existing control environment.

- 2.4 GSa/s, 16 bits, 750 MHz signal bandwidth

- 5 Vpp maximum amplitude

- Scalable up to 144 output channels

- Highest channel density available

- Less than 50 ns trigger-to-output delay

- Digital modulation at multiple frequencies

- LabOne® AWG Sequencer and Compiler

- Quantum computing

- Radar / Lidar

- NMR and EPR spectroscopy

- Semiconductor testing

- MIMO techniques in MRI and telecommunication

High-level AWG programming

Once the waveforms and sequences are defined in the LabOne AWG Sequencer, the LabOne AWG Compiler translates the instructions into machine language and transfers the result to the hardware in a minimum amount of time. LabOne sequencing supports loops with dynamically varying delay and conditional branching points.

In addition to the standard waveforms (such as Gaussian, Blackman, sinc, etc.), LabOne contains all essential math and array editing tools required for complex waveform design. It is possible to add, multiply, cut, and concatenate waveforms as well as to organize them in segments. Importing measured signals or waveforms calculated with MATLAB®, for instance, amounts to a simple drag-and-drop action.

With MDS, multiple HDAWGs can be operated as a single multi-channel AWG:

- Operation of all instruments from a single user interface or API

- Absolute synchronization of all output channels

- Phase locking of all instrument clocks

- Synchronization of time stamps and sampling rates for UHF instrument series

When multiple instruments are used, the LabOne AWG Compiler takes care of distributing the master sequence program across all instruments. An automated trigger exchange protocol ensures synchronized playback timing. With multi-device synchronization it is also possible to build up a complete signal generation and acquisition system that includes lock-in amplifier, boxcar, digitizer, and AWG functionality up to 600 MHz.

Oscillators, modulation, and phase control

The HDAWG is equipped with digital oscillators to generate the sinusoidal carrier of a signal independently of the programmed AWG envelope signal. This means that long signals can be generated with very fast waveform upload and precise phase coherence across many pulses. Carrier frequencies and phases that would otherwise be written to a static waveform can be freely adjusted and swept.

The HDAWG-MF Multi-Frequency option increases the number of oscillators and enables full digital I/Q modulation for frequency and phase modulation, frequency multiplexing, or phase cycling.

Low-latency triggering and sequence branching

Thanks to the low-latency design, the HDAWG is able to generate its first sample on the signal output less than 50 ns after detecting an external trigger on one of the trigger inputs on the front panel. This is essential for feedback experiments in quantum computing where device properties are short-lived, and each nanosecond that is saved improves the experimental outcome tremendously. The 4 or 8 output channels of the instrument can be grouped into units of 2 or 4. Each of these groups can then be triggered individually, which increases flexibility when distributing signals to separate parts of a setup.

In order to generate signals with a high complexity and real-time control, the HDAWG is able to select from up to 1024 pre-stored waveforms in a programmable memory based on the bit-pattern applied to its 32-bit digital input. These could represent a digital modulation pattern, a device-specific test waveform, or a multi-qubit state readout result.

Arbitrary waveform generator

Channels: 4 (HDAWG4 model)

8 (HDAWG8 model)

Vertical resolution: 16 bits

Waveform memory per channel: 64 MSa;

500 MSa (with HDAWG-ME option)

Sequence length: 8,192

Waveform granularity: 16 samples

Minimum waveform length: 32 samples

Sequencer clock frequency: Sampling rate divided by 8

Sequencer instructions (playback): Play waveform (single or multi-channel),

play waveform segment (start sample index and segment length),

play waveform from the library (DIO input state), interrupt waveform playback

Sequencer instructions (other): Wait constant, wait for trigger, set/get trigger state, set/get DIO state,

integer variable operations (add, subtract, logical operations),

change oscillator frequency/phase (real-time), change other

instrument setting (non real-time)

Sequencer control structures: Repeat (1 to 223-1 or infinite), conditional branch (multi-branch)

Wave Signal Output

Connector type: SMA (front panel, single-ended)

Output impedance: 50 Ω

Output coupling: DC

Output modes: Amplified, direct

Output range: ±0.1 V to ±2.5 V (amplified, into 50 Ω)

±0.4 V (direct)

Output level accuracy: ±(1% of setting + 5 mVpp) (amplified, into 50 Ω)

Output level resolution: < 0.1 mV

Offset voltage: 0.5 × peak voltage, max. ±1.25 V (amplified, into 50 Ω)

0 V (direct)

Offset voltage accuracy: ±(1% of setting + 5 mV)

Phase noise: < -135 dBc/Hz (amplified, 1 Vpp, 100 MHz, offset 10 kHz)

< -148 dBc/Hz (amplified, 1 Vpp, 100 MHz, offset 1 MHz)

< -135 dBc/Hz (direct, 0.5 Vpp, 100 MHz, offset 10 kHz)

< -148 dBc/Hz (direct, 0.5 Vpp, 100 MHz, offset 1 MHz)

Wave output period jitter: 3 ps RMS (square wave, 150 MHz)

Voltage noise

above 200 kHz: 35 nV/√Hz (amplified, ±2.5 V range, into high impedance)

12 nV/√Hz (direct, into high impedance)

RMS voltage noise

(integrated from 100 Hz to 600 MHz): 320 µVrms (amplified, ±2.5 V range, into 50 Ω)

100 µVrms (direct, into 50 Ω)

Time- and frequency-domain characteristics

Wave output bandwidth (-3dB, after correcting for sin(x)/x roll-off): 0 - 300 MHz (amplified, ±2.5 V range)

0 - 750 MHz (direct)

Sampling rate: 100 MSa/s to 2.4 GSa/s

Sampling rate divider: 20 to 213

Internal sampling clock resolution: 7 digits

Rise time (20% to 80%): 450 ps (0.2 V step, amplified, ±0.4 V range)

800 ps (1 V step, amplified, ±2.5 V range)

1100 ps (5 V step, amplified, ±2.5 V range)

300 ps (0.8 V step, direct)

550 ps (1 V step, amplified, ±1.5V range)

Overshoot: < 1%

Trigger delay to output: < 50 ns (within one channel pair 1&2, 2&4, 5&6, 7&8 using playWaveDigTrigger sequencer instruction)

< 180 ns (using waitDigTrigger sequencer instruction)

Skew between channels: < 200 ps

Skew control range: 10 ns

Skew control resolution

Marker and other outputs

Marker outputs: 1 per channel, SMA (front panel), 2 marker bits per waveform

Marker output impedance: 50 Ω

Marker output rise/fall time: 300 ps (20/80%)

Marker output period jitter: 60 ps p-p (square wave, 100 MHz)

Marker output skew control: -23...30 ns (range, at max. sampling rate)

~10 ps (resolution, at max. sampling rate, depends on absolute setting)

Sampling clock output: SMA on back panel

Sampling clock output amplitude: 0.8 Vpp (2.4 GHz into 50 Ω)

2.0 Vpp (1.0 GHz into 50 Ω)

Reference clock output: SMA on back panel

Reference clock output impedance: 50 Ω, AC coupled

Reference clock output amplitude: 1 Vpp (100 MHz into 50 Ω)

Reference clock output frequency: 100 MHz (internal reference mode)

10 / 100 MHz (external reference mode)

Reference clock output jitter: 260 fs RMS, derived from integrated phase noise measurement (12 kHz to 200 MHz offset frequency)

Inputs

Trigger inputs: 1 per channel, SMA (front panel)

Trigger input impedance: 50 Ω / 1 kΩ

Trigger input voltage range: ±5 V (50 Ω)

±10 V (1 kΩ)

Trigger input threshold range: ±5 V (50 Ω)

±10 V (1 kΩ)

Trigger input threshold resolution: < 0.4 mV

Trigger input threshold hysteresis: > 60 mV

Trigger input min. pulse width: 5 ns

Trigger input max. operating frequency: 300 MHz

Sampling clock input: SMA (back panel)

Reference clock input: SMA (back panel)

Reference clock input impedance: 50 Ω, AC coupled

Reference clock input frequency: 10 / 100 MHz

Reference clock input amplitude: -4 dBm to +13 dBm

Oscillators and clocks

Internal clock type: TXCO

Internal clock aging: ±0.8 ppm/year

Internal clock short-term stability: 0.0001 ppm (1 s)

Internal clock initial accuracy: ±1 ppm

Internal clock temperature stability: ±0..3 ppm (–20°C to +70°C)

Internal clock phase noise: -105 dBc/Hz (offset 100 Hz)

-125 dBc/Hz (offset 1 kHz)

Maximum ratings

Damage threshold Wave: -1.2 V / +1.2 V (direct)

-6 V / +6 V (amplified)

Damage threshold Mark: -0.7 / +4 V

Damage threshold Trig: -11 V / +11 V (1 kΩ input impedance)

-6 V / +6 V (50 Ω input impedance)

Damage threshold Reference Clk In: -4 V / +4 V (DC)

+13.5 dBm (AC, with DC offset 0 V)

Damage threshold Reference Clk Out: -4 V / +4 V (DC)

Damage threshold Sample Clk In: -4 V / +4 V (DC)

+13.5 dBm (AC, with DC offset 0 V)

Damage threshold Sample Clk Out: -4 V / +4 V (DC)

Damage threshold MDS In/Out: -0.7 / +4 V

Damage threshold DIO In/Out: -0.7 / +4 V (default configuration 3.3 V CMOS/TTL)

Connectivity and others

Digital IO (DIO): VHDCI 68 pin female connector,

32-bit, configurable as input or output, 3.3 V TTL

Host connection: LAN/Ethernet, 1 Gbit/s

USB 3.0, 5 Gbit/s

PC memory requirements: 4 GB+

PC CPU requirements: Compatibility with SSE2 instruction set required.

Examples: AMD K8 (Athlon 64, Sempron 64, Turion 64, etc.),

AMD Phenom, Intel Pentium 4, Xeon, Celeron, Celeron D,

Pentium M, Celeron M, Core, Core 2, Core i5, Core i7, Core i3, Atom

Operating system: See LabOne Compatibility

General

Dimensions: 43.0 × 23.2 × 10.2 cm

16.9 × 9.2 × 4.0 inch, suited for 19 inch rack

Weight: 4.6 kg; 10.2 lbs

Power supply AC line: 100−240 V (±10%), 50/60 Hz

Operating temperature: +5 °C to +40 °C

Operating environment: IEC61010, indoor location, installation category II, pollution degree 2

Operating altitude: Up to 2000 m